全文共6082字,预计阅读时间15分钟

作者 | 程韫韵(Emily)

编辑 | 谭舒雯(Poppy)

注:文中图片均来源于网络

前言

在人工智能高速发展的热潮下,庞大的数据量和复杂的算法模型对算力及芯片提出了新的需求。类脑芯片成为近年来学术界和产业界都越来越关注的重点方向,甚至在Gartner的芯片产业预测图中将类脑芯片判断为第三代人工智能芯片。上海新氦类脑智能科技有限公司(以下简称“新氦类脑智能”)就在此背景下诞生,类脑芯片及片上智能系统是新氦类脑智能的研发及商业转化的重点方向。近年来新氦类脑智能看到许多类脑芯片领域的创新突破和科研热潮,因此新氦类脑智能总结了类脑芯片领域的现状、问题和趋势,希望在充满信心的同时保持客观冷静分析,给行业的发展带来一些启发和推动作用。

近内存运算与存内运算

存算一体这一概念由来已久,最初被用在计算机系统结构领域,例如以相联存储器为核心的相联处理机(Associate Processor)。相连存储器带有信息处理功能,相联处理机要求存储单元能处理信息,一条指令可对多个数据同时执行逻辑运算。后来,存算一体这一概念逐渐被类脑计算领域采用,时识科技(SynSense)研发的类脑计算芯片就具备这一特征。随着神经科学的发展和超大规模集成电路的兴起,类脑计算芯片更加广泛地模仿以脉冲编码和存算一体为代表的交感神经元-突触结构和大脑的工作机制。一些模拟非易失性存储系统也被用来验证脉冲神经网络算法和非监督式学习,从而体现了存算一体芯片的潜力。

数据的爆炸性增长为新发现创造了机会,但也对计算力提出了史无前例的要求,例如从通用联网设备到仓储规模计算机日益增长的数据量、速度、多样性和准确性。通过工艺等比例缩小来扩展计算机处理能力的方法优势逐渐减小,而传统计算系统的限制,即“内存墙”“能耗墙”,在大数据快速增长的趋势下,使得对新范式的需求越发迫切。因此,Process in Memory(PIM)这个十多年前提出的概念重新在产业界和科研界获得广泛关注。PIM是指将计算单元如CPU和GPU放在离存储足够近的地方,从而降低数据传输的时延和成本。减少数据处理和数据存储间的距离可以更快地运行工作负载并得到结果。内存方面新的设计,如高带宽内存(HBM, High-bandwidth Memory)和混合内存立方体(HMC, Hybrid Memory Cube),以及处理单元阵列的广泛应用,如CPU和GPU,还包括FPGA和定制化的ASIC,都在PIM技术的发展和应用过程中起到了解决实用性和成本问题的作用。根据内存与逻辑元件的相对位置关系,现有的PIM可大致分为近内存运算(Near-Memory Computing)和存内运算(In-Memory Computing)。近内存运算的基本思想是将数据靠近计算单元,实现逻辑芯片内的存储计算;而存内运算是将处理任务带至存储内,在存储单元里做计算。这两种技术旨在加速系统的数据处理功能,或者搭建如神经网络等新的架构。[1]

近内存运算(Near Memory Computing)

图5 内存/存储层次结构

传统的存储层级如图5所示。其中,SRAM被整合到可以快速接入常用程序的高速缓存处理器中。DRAM用作主存储器单元,分离地存放在双列直插存储模块(Dual in-Line Memory Module, DIMM)中。磁盘驱动器和与非门固态存储驱动器(NAND-based SSDs)被用作存储器件。

相较于计算性能的发展,数据量增长得更快。在反复将数据在SSDs和CPUs之间传输的过程中,能耗和系统都面临挑战。解决方法之一是将处理器、内存和其他器件整合到传统的冯诺依曼结构中,按比例缩小这些组件,提升其性能,但会导致成本的增加和方程式的复杂化。另一种方法是将逻辑单元尽量靠近存储单元,从而实现芯片内的存储计算的近内存架构。

在内存附近处理任务的想法可以追溯到十九世纪六十年代,而近内存运算系统最早出现于十九世纪九十年代早期,如Vector IRAM (VIRAM)[2]。研究者设计了一种带有片上嵌入式DRAM(eDRAM)的向量处理器来开发多媒体应用数据的并行化处理。尽管研究颇有成效,但这些NMC系统并未渗透到市场。主要原因之一是当时的技术限制,存储器制造工艺和逻辑制造工艺不同,而且两者不兼容,能够与向量处理器整合的片上存储数量有限。

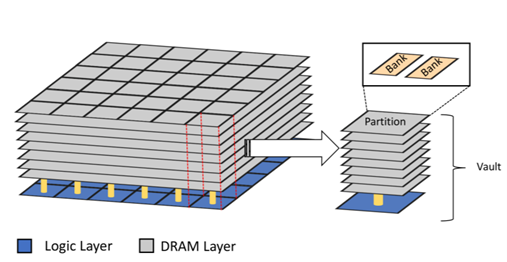

NMC的相关研究在大约二十年后重新获得广泛关注,主要原因有三个。首先,2.5D和3D堆叠技术的进步使逻辑和内存能够堆叠合并到一个封装里。先进的内存模组有美光科技的混合存储立方体(Hybrid Memory Cube,HMC)[3]、高带宽内存(High Bandwidth Memory,HBM)[4]和带宽引擎(Bandwidth Engine 2,BE2)[5]。如图6所示,美光科技的HMC通过硅通孔技术(through Silicon via,TSV)将数层DRAM放置在一层逻辑组件上。不仅提供了优于传统DDR DRAM的随机存取性能,还支持近内存操作,如读取修正写入和锁定。原因之二是,将计算移动到靠近数据存放处能够规避数据传输带来的性能和能耗限制。最后,现代数据密集型应用的蓬勃发展,如材料学、天文学、医疗健康等,亟需新的架构出现。[6]

图6 美光科技的混合存储立方体

存内运算(In Memory Computing)

得益于硅技术的发展,CMOS逻辑芯片可以用简单的二元信号完成复杂数据的处理,高集成度和小尺寸的优势让数字逻辑芯片占领了大量市场份额。然而,随着以RRAM和PCM为代表的新设备技术的成熟,被忽视已久的模拟神经计算在大规模应用中逐渐有了用武之地。虽然模拟电路连续信号处理的抗干扰性和计算精度不如数字运算,但基于存储的模拟运算在神经网络结构中可以实现更高的效率。

通过叠加欧姆定律乘法和基尔霍夫电流定律加法,作为神经网络计算基础的矩阵向量乘法(MVM)可以被映射到交叉阵列上,从而实现存内模拟运算。与MAC(Multiplicative Accumulation)不同,交叉阵列MVM可以在一个步骤内运行乘法和加法,与传统冯诺依曼结构相比节省了大量时间和能耗。忆阻器交叉阵列中存内运算的出现让模拟运算可以用于神经网络,并让类脑计算有了进一步发展。与传统高能耗的CMOS电路相比,电阻转换设备如同可以同时存储权重和传递信号的电子突触,更便于运行超低功耗的模拟存内运算。这种两端电阻设备可以同时实现数据存储和数据处理,提供对大多数AI应用至关重要的高数据吞吐量。目前,出于商业化的考量,电阻转换设备仍结合了传统硅计算组件。由于较低的热负载,电阻转换设备可以与CMOS基底兼容。芯片可以灵活地组成多种阵列,从而自动映射不同的神经网络算法来完成特定的计算任务。

脉冲神经网络(SNN)可以严格地模拟大脑信息处理机制,CMOS电路已被用于Intel Loihi、IBM TrueNorth等具有代表性的SNN芯片,但CMOS设备无法实现存储与计算的融合,从而会导致资源浪费。因此,找到具备模拟突触功能的人工突触设备尤为重要。首先,简单的两端忆阻器可以在面积、复杂度和能耗显著降低的情况下实现相似功能;FeFET中,铁电层的晶格极化能够模拟SNN的学习规则,例如STDP;还有一些创新低维材料也可用于SNN突触设备,例如用于具备STDP规则的非监督式学习的碳纳米管突触[7]。基于反向传播等算法,DNN可以通过新型存储技术部署在硬件设备中,而大多数专注于SNN设备拓展的研究还处于模拟阶段。然而,已有实验证明尽管类脑计算在技术成熟度上还处于早期阶段,未得到大规模应用,但它代表着AI芯片和存算一体的长期发展方向。

过去十年,新兴的非易失性存储(Nonvolatile Memory,NVM)技术取得了长足进展,例如转移随机存取存储器(Spin Torque Transfer RAM,STT RAM)[8]、相变存储器(Phase Change Memory,PCM)[9]和阻变随机存取存储器(Resistive RAM,RRAM)[10]。目前,主要厂商都具备了在关键技术节点上生产Gb量级设备的能力,包括美光45nm的1Gb PCM[11]、三星20nm的8Gb PCM[12]、东芝和闪迪联合研发的24nm 32Gb RRAM[13]、美光和索尼联合研发的27nm 16Gb导电桥式随机存取存储器(Conductive Bridge RAM,CBRAM)和由美光和英特尔联合研发的128Gb 3D XPoint技术[14]。

虽然取得了一定程度上的商业成功,但直接将这些技术直嵌入现有的电脑系统中效果不明显。从技术上看,这些技术的本质与主存储器或永久存储器不匹配,如单位成本、时延、能耗、耐久性和留存性。从经济角度看,尽管现有的存储器制造商获得了更多的投资用于新技术的研发生产,但很难说服终端用户在能够使用DRAM或闪存的情况下转向新产品,除非新产品能带来极大的好处。基于这种情况,一个可行的方法是开发非传统的模型架构。

目前学界对合并式逻辑存储器件的兴趣日益增强,旨在研发计算功能与存储器一体的计算架构。将数据从分离的存储单元传输到计算单元从时延和能耗上看非常昂贵。例如,机器学习中的单整数乘积累加(Multiply-Accumulate,MAC)操作仅需要约3.2pJ的能量,而如果权重值储存在片外的动态随机存取存储器(Dynamic Random Access Memory,DRAM)上,仅得到滤值就会耗费约640pJ能量,而且存储的能量要求比计算更高。这个问题在机器学习算法的训练阶段更为显著,因为有数以亿计的权重值需要学习并定期更新。为解决这个问题,Haensch提出电阻处理器(Resistive Processing Unit,RPU)的概念,模拟权重值被存放在交叉点设备中来最小化训练过程中的数据传输,合适的RPU能够以超过四倍的速度加速训练过程。[15]

机器学习中将权重数据与逻辑单元存放在一起还能够提升物联网边缘设备中复杂推断算法的性能。许多边缘系统中,出于隐私安全和时延的考量,推断过程需要在边缘端执行,并且严格的区域和能耗限制阻碍了有过多参数的机器学习模型的部署。

因此,新的研究项目或以系统为导向,或尝试利用除更好的亚阈值摆幅外,与新兴设备有关的特性。一些设备显示出适用于新兴计算架构的特性,例如逻辑设备的非易失性、可重构性和高计算密度。合并式逻辑与存储组件是一种从架构层面开发设备特性的方法,并且能够满足应用层面的需要。

尽管存内运算还没有一个普遍认可的准确定义,但已经广泛应用到不同领域。例如,数据库中存内运算用于开发超高速缓存,芯片制造商正研发能够在神经网络存储内处理任务的芯片,其他应用还包括神经形态计算。存内运算架构大致可分为四类,首先是利用交叉结构的点积功能加速矩阵乘法。矩阵乘法是许多应用的计算核心,如深度学习和优化等,代表性成果是PRIME[16]、ISAAC[17]和忆阻玻尔兹曼机[18]。忆阻玻尔兹曼机是一类基于电阻随机存取存储器技术,以内存为中心,大规模平行的硬件加速器,用于大规模组合优化和深度学习。通过利用RRAM的电气性能实现内存阵列内就地、细粒度的平行计算,忆阻玻尔兹曼机能够降低对内存单元和计算单元间数据传输的需要。两类经典的优化问题,图划分与布尔可满足性,和深度信念网络应用可以映射在这类硬件上。相较于多核系统,忆阻玻尔兹曼机能够实现57倍高的性能和二十五分之一的能耗,并且几乎不存在优化问题答案质量下降的问题。与基于PIM系统的电阻随机存取存储器相比,忆阻玻尔兹曼机分别有约七倍高的性能和五分之一的能耗[19]。其次是在神经形态系统的突触网络中利用NVM阵列的模拟特性来模仿人脑模糊、容错和随机的计算过程,并伴随着空间和能耗上的优势。第三种是相联处理机(Associative Processor,AP),即非易失性内容可寻址存储器(Nonvolatile Content Addressable Memory,nv-CAM)或三态内容可寻址存储器(Ternary Content Addressable Memory, nv-TCAM),能够支持相联检索并通过内容而非地址定位数据记录。代表性的研究成果包括基于RRAM的TCAM[20]、AC-DIMM[21],和基于RRAM的相联处理机[22]。CAMs和TCAMs作为网络路由器有明显的优势,能够支持新兴的机器学习模型如多维计算(Hyperdimensional Computing, HDC)和用外部内存增强的神经网络。在路由器内,CMAs/TCAMs元件被用来搜索媒体访问控制(Media Access Control, MAC)的匹配。最后一类是可重构架构(Reconfigurable Architecture,RA),代表性研究有非易失性现场可编程门阵列(Nonvolatile Field Programmable Gate Array,nv-FPGA)[23],和结合了TCAM和FPGA二者优点的可重构存内运算架构[24]。FPGA是由通过可编程互联连接的可配置逻辑块矩阵构成的半导体器件,在制造完成后能够根据所需的应用或功能要求进行重新编辑,支持对设备中大量电气功能进行更改,这是FPGA区别于特定用途集成电路(ASIC)的关键。FPGA能以更低的价格实现逻辑密度增加和众多其他特性,如嵌入式处理器、DSP模块、时钟技术和高速串行。AP和RA在存内处理方面有巨大潜力,无需高成本。它们不像第一二类需要昂贵的混合信号电路(A/D,D/A),使用门槛也更低。尽管如此,这四种架构都面临着一个关于操作鲁棒性的常见问题,即NVM技术有限的ON/OFF电阻比。这一问题能够从材料工程、元件设计和编码技术等方面得到一定程度的减轻。[25]

趋势展望

PIM为克服数据密集型应用带来的挑战提供了可行的办法。与存内运算相比,近内存运算的使用门槛更低,因为无需改变原有的计算结构,而存内运算将会最大程度上开发利用内存带宽来实现更多的平行计算。目前,PIM研究领域还存在一些开放性问题,关系到未来的研究方向。首先,哪一种新兴内存技术将会最大程度地支持近内存运算架构这一点还不清楚。例如,大量研究专注于三维堆叠DRAM和非易失性存储如PCM、ReRAM和MRAM,这些新技术的未来依赖于耐久性、可靠性、成本和密度各个方面的提升。三维堆叠还需要独特的能耗和热量解决办法,因为传统的散热器技术无法支撑更多的靠近内存的计算。大多数架构没有考虑到三维堆叠内存严格的能耗预算,这会限制架构的实用性。DRAM和NVM有不同的存储性质,混合设计能够为现有的系统带来变革。其中,整合了CPU、DRAM和基于闪存的NVM的三维异构存储结构能够满足大数据应用的存储需求,如大容量、短时延和高带宽。因此,异构近内存处理成为了具有高潜力的新研究领域。大多数架构专注于计算层面,极少数具备一致性和虚拟内存支持,而缺少一致性和虚拟内存会增加编程的难度,阻碍这一范式的应用。在应用层面,出于能效的考虑,算法的代码和数据需要位于同一个地方。例如,HMC算法需要避免数据在不同的内存模组间过多的移动。当室间数据传输不可避免时,应采用轻量级的数据迁移机制。近内存运算元件之间的互联网络需要更多地从定量的角度进行研究。近内存元件与新兴互联标准的相互作用在提升运行在NMC服务器上的大数据的性能和能耗方面十分重要。存内运算主要面临高价、处理不同类型数据的能力和整合分离数据源的能力等问题,而未来存储解决方案的主要特征有能量功耗、成本、上市时间、密度和性能等。NAND、3D NAND、PCRAM、STT-RAM和ReRAM可以作为DRAM的替代品,而使用DDP和TSV作为DRAM的替代方法存在价格上的争议,TSV的预计成本比DDP还高22%[26]。非易失性内存和能够提供通用接口的混合存储模型将会成为首选的存储方法。

声明:本文章发布目的在于传递更多信息,并不代表本公众号赞同其观点和对其真实性负责。如涉及作品内容、版权和其它问题,请及时与我司联系,我们将在第一时间处理!

/

程 韫 韵 Emily

/

新氦类脑智能战略总监,复旦-麻省理工学院国际工商管理硕士,拥有多年跨区域、跨行业的企业战略咨询经验。在类脑智能、人工智能技术及应用落地方向有深入的行业分析和市场洞察,为政府、企业提供数智化转型咨询服务,为AI创业团队提供商业落地建议。主导撰写AI技术白皮书,类脑芯片白皮书。

沪公网安备 31011002003093号

沪公网安备 31011002003093号